**УО «Гомельский государственный университет

имени Франциска Скорины», Беларусь**

## **ИСПОЛЬЗОВАНИЕ ДИЭЛЕКТРИЧЕСКИХ ЗОЛЬ-ГЕЛЬ ПЛЕНОК ДЛЯ ФОРМИРОВАНИЯ КНИ-СТРУКТУР**

На протяжении последних лет ведущие производители нано- и микропроцессорных структур, такие как Advanced Micro Devices (AMD) и International Business Machines (IBM), при производстве своих процессоров используют структуры типа кремний на изоляторе – КНИ (англ. Silicon on insulator – SOI)[1–2].

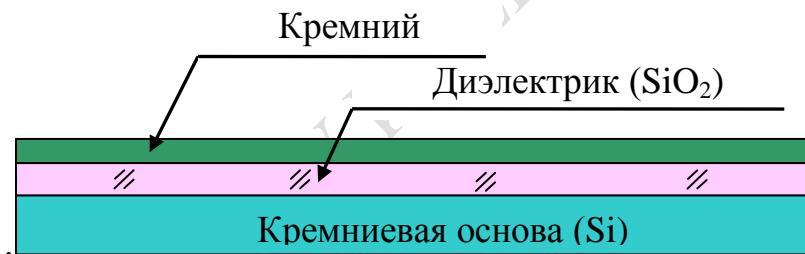

Структура, выполненная по технологии КНИ, представляет собой трёхслойный пакет, который состоит из монолитной кремниевой пластины, диэлектрика и размещённого на нём тонкого поверхностного слоя кремния (рисунок 1).

**Рисунок 1 – Схема КНИ-структуры**

В качестве диэлектрика может выступать диоксид кремния  $\text{SiO}_2$  или, гораздо реже, сапфир (в этом случае технология называется «кремний на сапфире», или КНС). Наибольшее распространение получили КНИ-структуры, где в качестве изолятора выступает диоксид кремния. Для создания таких диэлектрических структур в основном используются такие методы, как PVD (Physical Vapour Deposition); CVD (Chemical Vapor Deposition). Данные методы обладают рядом недостатков: высокими энергозатратами, сложными циклами производства, наличием дефектов в рабочих слоях.

За последние годы метод химического осаждения из растворов стал широко использоваться в современной микроэлектронике, что обусловлено возможностью создания материалов сложного химического состава и структуры, а также получения покрытий особой чистоты [3]. Одним из таких методов является золь-гель метод. При получении КНИ

структур в качестве слоя диэлектрика используется  $\text{SiO}_2$  покрытие, полученное золь-гель методом. Этот метод является одним из перспективных методов синтеза различных диэлектрических, изолирующих и защитных материалов, метод не требует емкого оборудования, является гораздо более экономичным и экологически чистым, чем PVD и CVD методы. Процесс формирования диэлектрической силикатной пленки состоит из трех важнейших для ее физико-химических свойств стадий: получение однородного золя в растворе из исходных компонентов; нанесения золя на подложку монокристаллического кремния методом центрифугирования; формирование оксидной диэлектрической пленки путем термообработки.

Пленкообразующий раствор был приготовлен на основе композиций органических соединений кремния. Созревание золя длятся 2–3 суток при комнатной температуре. Прочность и адгезионные свойства покрытия определяется правильным подбором соотношения компонентов раствора. Перед нанесением пленкообразующий раствор помещали в ультразвук для деполимеризации в нем высокомолекулярных соединений, что улучшало качество получаемых покрытий. Пленкообразующий раствор наносили на поверхность монокристаллического кремния марки КЭФ-45 ориентации (100) методом центрифугирования при относительной влажности воздуха 90 %. В результате были получены однородные покрытия, не имеющие дефектов в своей структуре. После нанесения образец помещается в печь и термообрабатывают при температуре от 300 до 500 °C на воздухе 5–10 минут. Толщину покрытия можно варьировать при помощи вязкости исходного пленкообразующего раствора, частоты вращения центрифуги (1000–5000 об/мин). В результате толщина диэлектрической пленки может быть задана в пределах 0,1–0,2 мкм до 4,0–5,0 мкм.

Для исследования стойкости к механическому истиранию и диэлектрических свойств было подготовлено несколько образцов с подслоем термического окисла и без него:

- Д-1 пластина с подслоем термического окисла + слой диэлектрика;

- Д-2 пластина с подслоем термического окисла + слой диэлектрика;

- Д-3 пластина с одним слоем диэлектрика;

- Д-4 пластина с одним слоем диэлектрика.

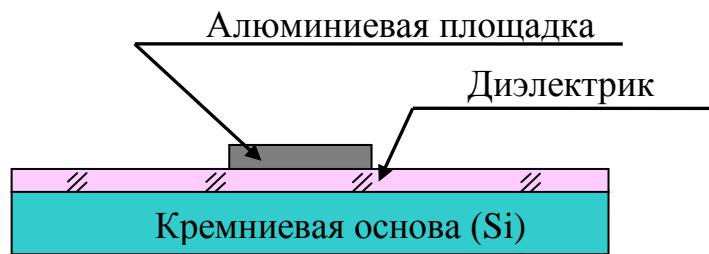

Для измерения диэлектрических свойств на поверхности данных покрытий, вакуумными методами, были сформированы алюминиевые площадки (рисунок 2).

Рисунок 2 – Диэлектрическое покрытие с алюминиевыми площадками

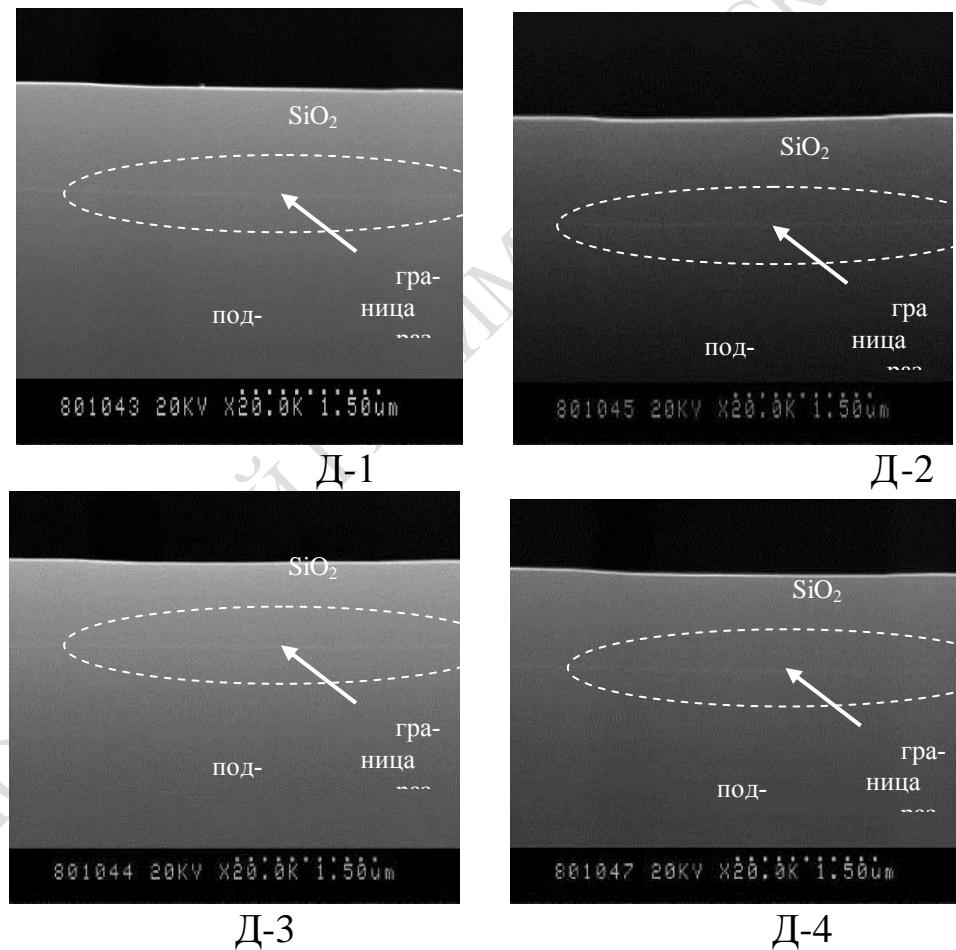

На рисунке 3 представлены изображения РЭМ-скола полученных образцов. Можно увидеть, что диэлектрические пленки имеют однородную структуру, термический окисел имеет толщину от 10 до 20 нм.

Рисунок 3 – Изображение РЭМ-скола золь-гель  $\text{SiO}_2$  диэлектрических пленок на поверхности монокристаллического кремния (образцы Д-1, Д-2, Д-3, Д-4)

Результаты измерения диэлектрических свойств, показателя преломления и толщины полученных покрытий представлены в таблице 1.

Таблица 1 – Электрофизические параметры диэлектрических слоев

| № образца | Показатель преломления | Толщина слоя по РЭМ-сколу, мкм | Диэлектрическая проницаемость |

|-----------|------------------------|--------------------------------|-------------------------------|

| Д-1       | 1,42                   | 0,94                           | 8,2                           |

| Д-2       | 1,439                  | 1,04                           | 7,44                          |

| Д-3       | 1,462                  | 0,93                           | 4,42                          |

| Д-4       | 1,401                  | 1,01                           | 5,8                           |

Из таблицы видно, что величина показателя преломления на образцах Д-1, Д-4 составляет 1,4–1,42, что близко к величине показателя для термического окисла равной 1,42. Для образцов Д-2, Д-3 величина показателя преломления составляет 1,439–1,462, что несколько превышает величину показателя для термического окисла. Наличие подслоя термического окисла не оказывает влияния на толщину полученных покрытий, которая варьируется от 0,93 до 1,04 мкм. Это связано с тем, что толщина термического окисла на несколько порядков меньше толщины полученных диэлектрических  $\text{SiO}_2$  покрытий. Величина диэлектрической проницаемости слоев находится в диапазоне 4,4–8,2, что превышает ее значение для термической двуокиси кремния равное 3,8.

Полученные диэлектрические  $\text{SiO}_2$  покрытия устойчивы: к термическому воздействию; к травлению в стандартном травителе для алюминия, разогретого до температуры  $T=40$  °С в течении 20 минут; обладают механической стойкостью к истиранию (3000 циклов истирания).

На поверхности данных покрытий, вакуумными методами, могут быть сформированы тонкие слои металлов и полупроводников без изменения электрофизических и физико-химических свойств диэлектрического  $\text{SiO}_2$  подслоя.

### Литература

1. Design methodology for the IBM POWER7 microprocessor / Friedrich J., Puri R., Brandt U. [et al.] // IBM Journal of Research and Development. – 2011. – Vol. 55. – P. 1–14.

2. An x86-64 Core in 32 nm SOI CMOS / Jotwani R., Sundaram S., Kosonocky S. [et al.] // Solid-State Circuits, IEEE Journal. – 2011. – Vol. 46. – P. 162–172.

3. Васильев, В.А. Изолирующие слои многоуровневой разводки интегральных схем с низкой диэлектрической проницаемостью / В.А. Васильев, К.А. Воротилов, А.С. Сигов // Электронная промышленность. – 2004. – № 4. – С. 145–153.